文章摘要

【关 键 词】 人工智能、高性能计算、异构集成、芯片技术、AI工作负载

2022年,ChatGPT的推出推动了人工智能(AI)和高性能计算(HPC)应用的指数级增长,使得AI在日常生活中的重要性日益增加。大型AI模型虽然擅长处理复杂任务,但它们需要大型训练数据集和大型计算系统,导致芯片尺寸增大、功率密度提高,设计节能架构变得更加困难。因此,芯片的异构集成(HI)变得至关重要,它能够实现高系统吞吐量和能源效率,满足不断增长的计算需求。通过将片上系统(SoC)拆分为多个Chiplet并集成到单个封装中,可以提高系统的设计灵活性、功能性、带宽、吞吐量和延迟。

半导体公司如Nvidia、Intel和AMD已经利用HI技术运行实时生成式AI模型并训练具有数十亿个参数的大型语言模型(LLM)。HI技术通过将高带宽内存(HBM)、CPU和GPU等芯片集成到一个封装中,显著提高了吞吐量、延迟和能效,克服了传统2D单片芯片设计的局限性。

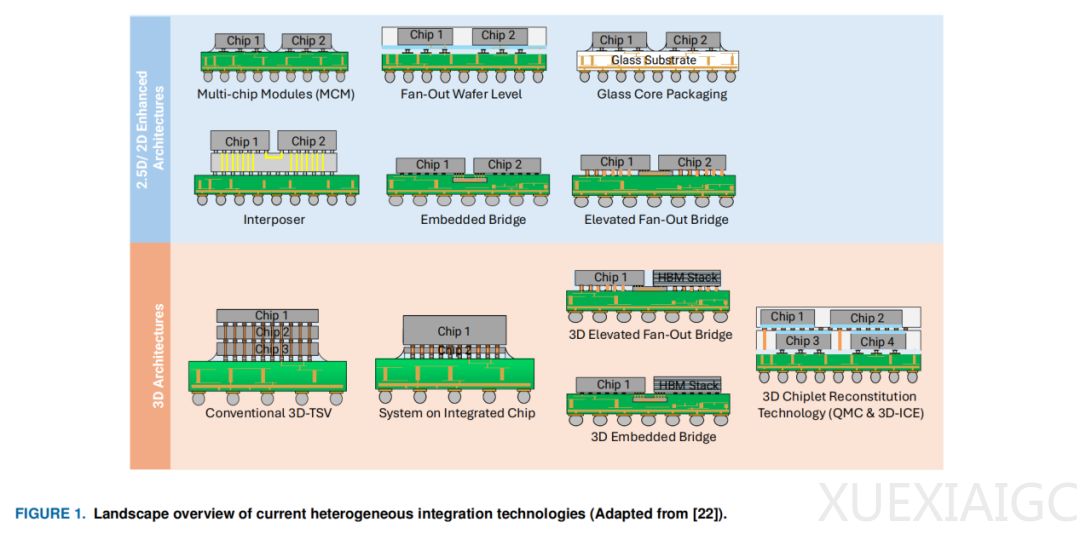

当前和新兴的HI技术根据IEEE电子封装协会(EPS)异构集成路线图的定义,将multi-die架构分为2D、2.5D或3D。多芯片模块(MCM)是最早的多芯片2D架构之一,但互连密度可能受到限制。2.5D架构利用玻璃、硅中介层或局部硅桥等基板提高互连密度。晶圆级封装(WLP)技术对于基于先进芯片的架构具有重要意义,因为它们可以实现高互连密度、减少互连延迟和增加带宽。3D HI技术使用TSV和细间距互连技术实现高带宽和低延迟系统。

人工智能的快速发展推动了HI架构的多种商业部署,这些架构专门用于加速最大的人工智能工作负载。Cerebras、Nvidia、AMD、Intel和Tesla等公司最近为高计算AI工作负载设计的HI架构的商业部署被调查。芯片间接口和通信协议随着系统中芯片数量的增加变得越来越重要,UCIe协议已开始成为通用行业标准。

玻璃芯封装的最新进展被总结,评估了它们的优点和局限性。基于玻璃的中介层通过提高信号完整性、支持高密度互连、集成光通信、优化热管理以及确保可靠性和可扩展性,增强了用于AI应用的半导体封装的带宽能力。玻璃表面光滑,可以实现细线和空间的缩放,这对于实现非常高密度的互连至关重要。然而,玻璃基板的易碎性和相对较低的散热性带来了挑战。尽管如此,玻璃芯封装因其多种优势而受到关注,特别是在AI和HPC应用中。

原文和模型

【原文链接】 阅读原文 [ 5427字 | 22分钟 ]

【原文作者】 半导体行业观察

【摘要模型】 moonshot-v1-32k

【摘要评分】 ★★★★★