文章摘要

【关 键 词】 HBM技术、AI芯片、市场竞争、内存解决方案、技术规格

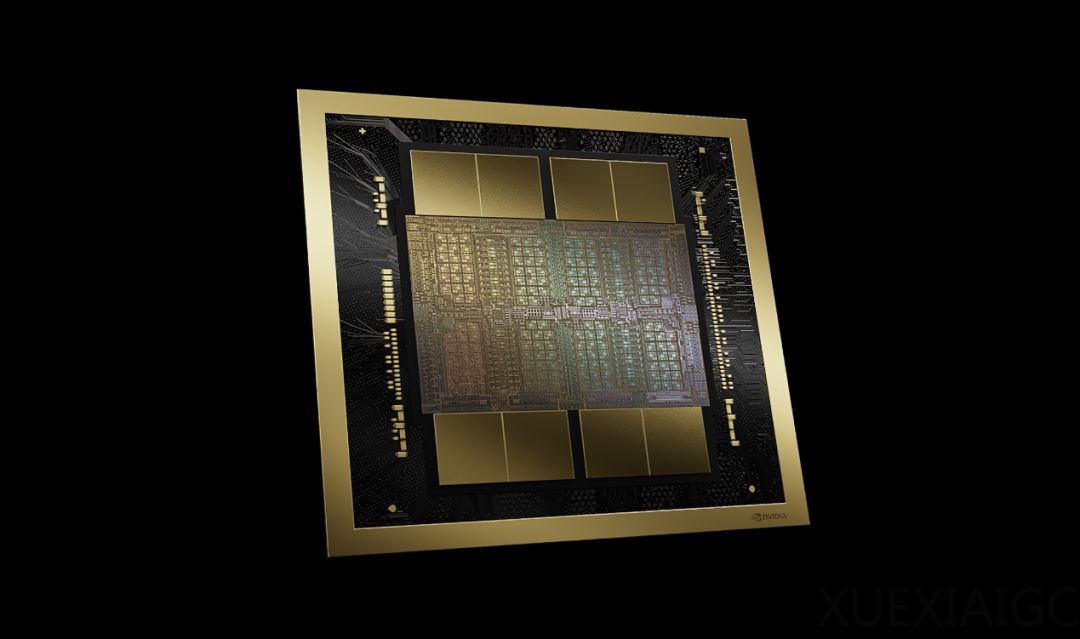

随着人工智能和高性能计算需求的不断增长,高带宽存储器(HBM)技术在内存行业中备受瞩目。尽管内存市场普遍面临亏损,但HBM市场却持续走高,特别是海力士作为英伟达H100的HBM供应商,成为AI浪潮中盈利颇丰的厂商之一。目前,尽管HBM 3E发布仅一年左右,SK海力士和三星这两家韩国厂商已开始围绕HBM4的量产展开激烈竞争,计划于10月和11月完成基本设计并进入量产阶段,以期在AI芯片市场占据主导地位。

HBM4技术规格相较于HBM3E有显著提升,提供了双倍的通道宽度,从2048位提升至1024位,数据传输速度和性能均得到增强。HBM3E堆叠了12个DRAM芯片,支持24GB和32GB容量,而HBM4则可堆叠16个DRAM芯片,支持64GB容量。JEDEC表示,HBM4旨在提高数据处理速度,同时保留更高的带宽、更低的功耗和更大的单个芯片或堆栈容量等关键特性,这对于需要高效管理大型数据集和复杂计算的应用至关重要。

HBM技术标准的争夺一直是技术路线之争的焦点。海力士和三星都希望将标准化为己用,通过与内存和逻辑制造商共同设计芯片,再由晶圆代工厂制造。而美光则主张通过HBM-GPU组合芯片获得更快的内存访问速度,但这种依赖单一厂商的策略存在较大风险。随着机器学习训练模型的增大和训练时间的延长,加快内存访问速度和提高每个GPU内存容量的需求愈发迫切。

SK海力士副总裁柳成洙在首尔举办的“SK利川论坛2024”上公布了公司的战略,即开发一款性能比现有HBM高出30倍的产品。柳成洙强调,公司专注于通过先进的执行能力,以面向AI的内存解决方案来应对大众市场。SK海力士的HBM受到全球公司的高度关注,尤其是七大科技巨头(M7),包括苹果、微软、谷歌Alphabet、亚马逊、Nvidia、Meta和特斯拉等。柳成洙表示,公司需要自己定义内存规格,而不是跟随其他公司。

为了实现HBM4的量产,SK海力士与台积电组建了AI半导体联盟,结合双方在各自领域的优势,协调战略。台积电将使用12FFC+(12nm级)和N5(5nm级)工艺技术协助海力士生产HBM4芯片。台积电的N5工艺可实现更多集成逻辑和功能,互连间距从9微米缩短至6微米,这对于片上集成至关重要。同时,台积电还在优化其封装技术,特别是CoWoS-L和CoWoS-R,以支持HBM4集成。

三星作为拥有晶圆代工、存储器、封装等能力的IDM企业,也在积极推动定制化的HBM AI解决方案。三星电子内存部门新事业企划组长崔章锡表示,公司打算为HBM4代开发多种定制化的HBM内存产品,并宣布与AMD、苹果等大客户展开合作。三星的计划是以HBM4为契机扭转HBM战局中的劣势,利用系统LSI部门和代工部门的内部合作,从HBM4基础芯片的初始设计开始优化性能。

混合键合技术成为内存市场的焦点,这项技术能够减少HBM厚度并提高速度,被认为是决定市场成败的关键技术。SK海力士正在开发预计明年量产的HBM4的两种键合方式,包括现有的MR-MUF和混合键合的双轨方式。混合键合技术无需在DRAM之间使用凸点,直接连接DRAM,大幅减少HBM的厚度,缩短DRAM之间的距离,加快数据传输速度。三星电子也在尝试颠覆HBM市场的动向,非常决心在HBM4中实现混合键合的成功。

目前,HBM市场已形成“一超一强一平”的格局。海力士技术实力雄厚,作为英伟达最重要的供应商,掌握着主动权。三星尽管在HBM3和3E的英伟达认证上表现不理想,但在HBM4上不容有失。美光虽然已向英伟达出货HBM,但市场份额较小,对HBM标准的影响有限。随着HBM4的到来,行业将迎来更激烈的竞争,胜者有望主宰未来十年的DRAM市场。

原文和模型

【原文链接】 阅读原文 [ 4186字 | 17分钟 ]

【原文作者】 半导体行业观察

【摘要模型】 moonshot-v1-32k

【摘要评分】 ★★★★★