文章摘要

NEO 半导体公司近期宣布了两项全新的 3D X-DRAM 单元设计——1T1C 和 3T0C,这些设计有望彻底改变 DRAM 内存的现状。预计这两项技术将在 2026 年进行概念验证测试芯片的研发。基于现有的 3D X-DRAM 技术,新设计的单个模块可容纳 512 Gb(64 GB),是目前市售模块容量的 10 倍。测试模拟显示,新技术的读/写速度达到 10 纳秒,数据保留时间超过 9 分钟,这两项性能均处于当前 DRAM 技术的前沿。

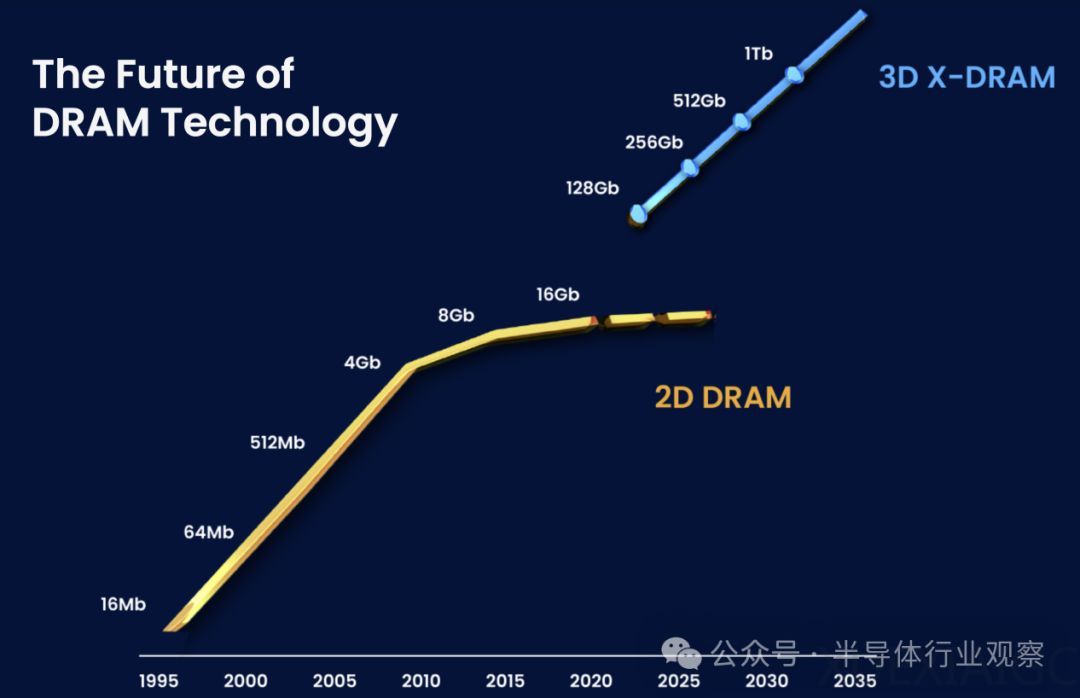

NEO 公司指出,推出这些新技术的背景是 DRAM 行业在 10 纳米技术节点以下遭遇了电容器尺寸缩小的瓶颈。尽管开发 3D DRAM 工艺极其复杂,但单片 3D DRAM 阵列的需求日益迫切。1T1C 和 3T0C 设计被视为变革性解决方案,旨在为高密度、高功率效率和高可扩展性的数据应用提供支持。

1T1C 设计集成了一个电容器和一个晶体管,采用类似 3D NAND 的结构以降低制造成本,同时利用 IGZO(铟镓锌氧化物)沟道来增强数据保留能力。IGZO 以其极低的关断电流著称,能够显著延长存储时间。电容值由单元尺寸决定,仿真结果显示,1T1C 单元在 128 层以上的 3D 阵列中仍能保持可靠的感测电压。此外,通过添加隔离层,1T1C 设计可以堆叠超过 512 层单元,进一步提升了可扩展性。

3T0C 设计则集成了三个具有 IGZO 通道的晶体管:写入晶体管、读取晶体管和存储晶体管。存储晶体管通过在其栅极中保存电子来保留数据,从而实现电流感应。这种设计不仅适用于 DRAM 应用,还特别适合内存计算和人工智能(AI)应用,能够满足高速数据处理和高效电源管理的需求。

NEO 强调,新推出的 DRAM 技术具有多项优势:无与伦比的保留时间和效率,得益于 IGZO 通道技术,1T1C 和 3T0C 单元的保留时间长达 450 秒,显著降低了刷新功率;制造友好,采用改进的 3D NAND 工艺,只需少量改动即可实现完全可扩展性;超高带宽,通过独特的阵列架构进行混合绑定,显著提高内存带宽并降低功耗;适用于高级工作负载的高性能,专为人工智能、边缘计算和内存处理设计,具有可靠的高速访问和降低的能耗。

3D X-DRAM 技术基于创新型无电容浮体单元(FPC),利用现有的 NAND 工艺制造类似 3D NAND 的阵列,与其他 3D DRAM 解决方案相比,具有更高的可扩展性和经济性。此外,这些设计无需硅通孔(TSV),支持混合键合技术,可将带宽提高 16 倍,同时显著降低功耗和发热量,成为 AI 应用的变革性创新。

NEO 半导体公司创始人兼首席执行官 Andy Hsu 表示,1T1C 和 3T0C 3D X-DRAM 的推出正在重新定义内存技术的可能性,突破了当今 DRAM 的扩展限制。随着 3D X-DRAM 技术平台的不断完善,NEO 公司为现代和新兴应用提供了卓越的容量和带宽解决方案。

原文和模型

【原文链接】 阅读原文 [ 2866字 | 12分钟 ]

【原文作者】 半导体行业观察

【摘要模型】 deepseek-v3

【摘要评分】 ★★★★★