文章摘要

【关 键 词】 DAC会议、RigorFlow 2.0、RigorCons、数字后端签核、芯片设计自动化

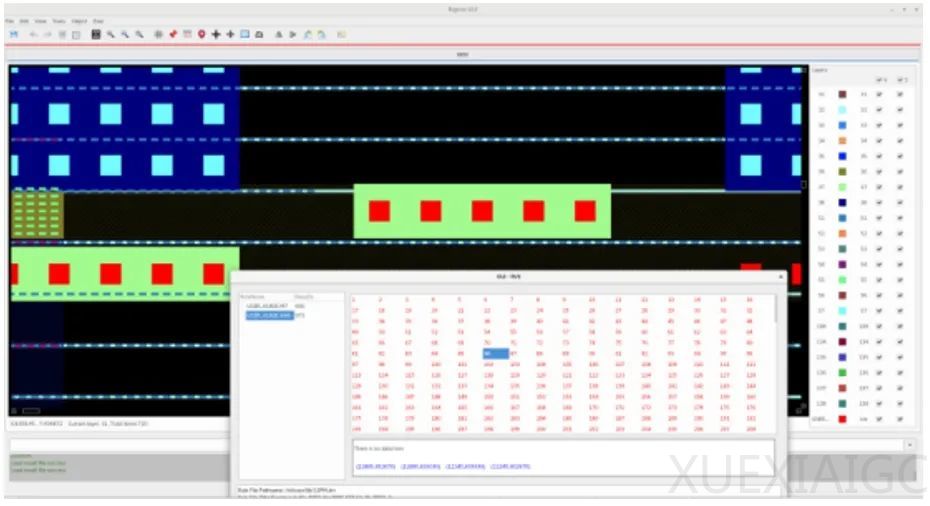

2024年6月,全球电子设计自动化盛会DAC将在上海举行,届时上海日观芯设自动化有限公司(Rigoron)将展示其全新升级的一站式数字后端签核工具系列。此系列产品包括:IC设计全流程管理软件RigorFlow 2.0、时序约束验证与管理软件RigorCons、静态时序分析软件RigorTime、物理验证及签核软件RigorDRC以及功耗分析及签核软件RigorEMIR。

RigorFlow 2.0已成功进入批量商用阶段,并在业界领先芯片设计厂商中试用。该软件旨在解决集成电路设计流程中的多种难题,并提升IC设计工程师和团队的管理效率。其主要升级内容包括实时数据存储与可视化统计分析功能,帮助用户比较不同设计方案的性能和效率,从而做出更科学的设计决策。

同时,RigorCons和RigorDRC正处于业内领军芯片设计厂商的重点试用中,标志着日观芯设在数字后端签核和芯片设计自动化领域的持续创新和发展。这些进展预示着公司为未来芯片设计领域带来更高性能的设计验证解决方案,并为技术创新开辟新的可能性。

在即将到来的DAC会议上,日观芯设将向来自世界各地的头部芯片设计厂商展示其最新的产品和技术。公司希望借助此次会议与业界专家和客户进行深入交流,分享最新的研发成果,同时也寻求新的合作机会和市场共赢的可能。

原文和模型

【原文链接】 阅读原文 [ 1697字 | 7分钟 ]

【原文作者】 半导体行业观察

【摘要模型】 generalv3.5

【摘要评分】 ★★★★☆

© 版权声明

文章版权归作者所有,未经允许请勿转载。

相关文章

暂无评论...