文章摘要

【关 键 词】 3D-IC设计、散热问题、异构芯片、多芯片集成、EDA工具

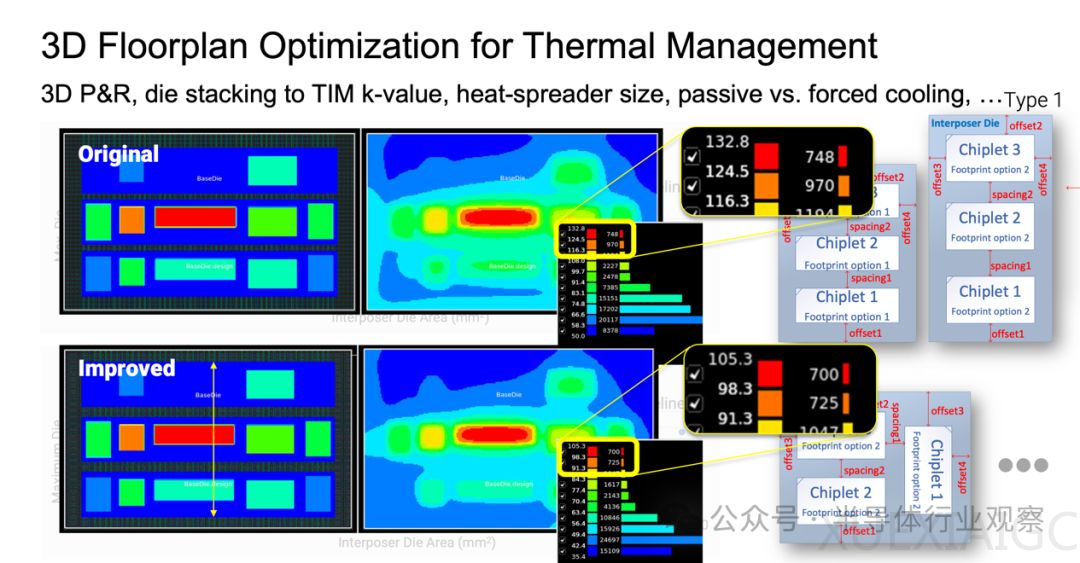

随着3D-IC和异构芯片技术的发展,自动缓解热问题成为设计中的首要任务。散热问题在3D-IC设计中尤为突出,因为逻辑芯片堆叠在一起会产生大量热量,而传统的散热方式如散热器或基板在3D-IC中不再适用。因此,需要在设计阶段就考虑如何将热量分散到整个芯片上或限制在可以有效去除热量的区域。

芯片制造商已经开始采用逻辑上逻辑和内存上逻辑的设计方式,以应对平面缩放成本的增加。Yole预测,从2025年开始,大多数服务器芯片将使用小芯片构建,超过50%的批量客户端PC将使用小芯片。这增加了对适应工具和工作流程的需求。

布局规划、布局、时钟和布线是布局布线流程的四个主要阶段。在布局规划阶段,设计师将大型功能模块放置在芯片的不同区域,确定连接性。然后,标准单元作为定义的模块放置在每个边界内,并根据本地连接通过互连相互布线。这一过程需要考虑多芯片集成、异构技术的潜力,并管理高密度芯片间互连的复杂性。

在3D-IC设计中,必须考虑到每个维度,包括z轴上的耦合效应、电阻率和跨芯片的时序路径。此外,由于金属层之间的高导电性,堆叠的金属连接可能会产生烟囱效应,导致高功率密度区域出现非常高的散热量。因此,热效应尤其是3D结构中的热串扰对设计团队的工作方式产生了重要影响。

热规划在物理设计中至关重要,因为大多数高性能CPU都具有加速和功率节流功能,以管理硬限晶体管结温,确保芯片可靠性。减少热传感器之间的节流裕度对于测量最关键工作负载引起的热点非常重要。此外,瞬态热功率斜坡建模和内部模拟调整温度敏感参数(如泄漏)也是必要的。

EDA公司鼓励用户在设计流程的早期进行建模,以确保减少第一次通过后的迭代。新的抽象方法和设计引擎正在开发中,以处理多芯片和多维结构。人工智能也被整合到EDA工具中,以提供预测智能并优化设计。

总之,3D-IC和异构芯片设计面临着散热、多物理效应和多芯片集成等挑战。设计人员需要采用新的工具和方法,以实现热感知布局和布局规划,同时考虑多物理模拟和多芯片协同优化。随着技术的发展,EDA工具和设计方法也在不断进步,以满足日益增长的设计需求。

原文和模型

【原文链接】 阅读原文 [ 3416字 | 14分钟 ]

【原文作者】 半导体行业观察

【摘要模型】 moonshot-v1-32k

【摘要评分】 ★★★★★