文章摘要

【关 键 词】 异构集成、芯片互连、封装技术、D2D接口、系统发现

随着系统级芯片(SoC)的分解,行业正在探索如何将这些分解后的组件以异构方式重新组合。这一过程得益于互连技术、复杂分区的进步,以及对可行方案的深入理解。尽管即插即用的理念未变,但实现过程比预期复杂,受应用程序、工作负载、封装类型、AI集成、软件需求和互连类型等多种因素影响。

Arm的系统架构师Rob Dimond强调,互连技术是连接各部分的粘合剂,包括片上网络(NoC)、芯片内互连以及跨芯片的UCIe连接。Cadence的Arif Khan指出,chiplet互连的挑战在于如何分解计算和数据流,以及架构设计。Blue Cheetah的Elad Alon提到,线路数量和特性的差异推动了设计方法的变化,而2.5D或3D封装技术提供了操作空间,但设计决策通常基于隔离跨芯片时序接口的需求。

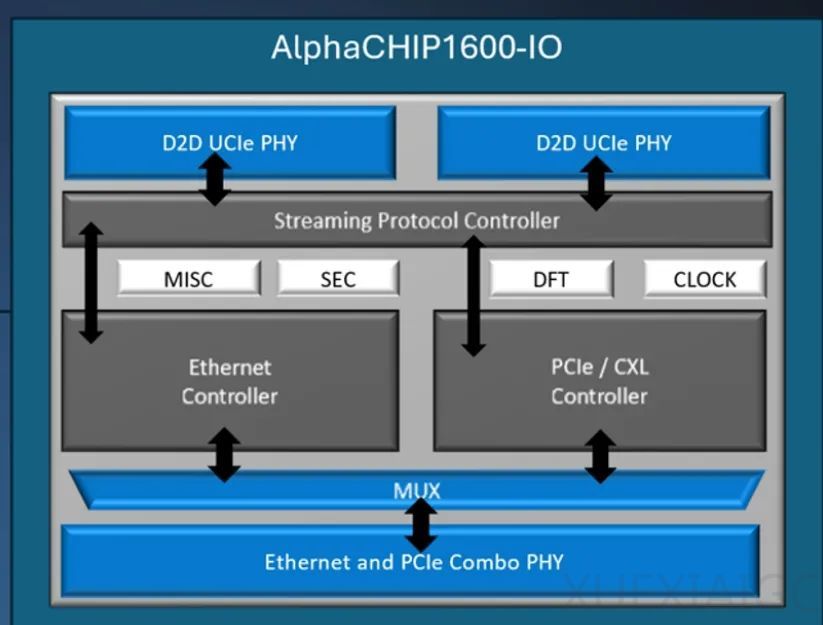

芯片互连与SoC互连不同,它们通常封装成通信协议,而非片上总线。Arteris的Ashley Stevens解释,芯片互连允许数据通过宽接口以分组格式传输,需要支持各种边带信号。Alphawave Semi的Letizia Giuliano强调,chiplet需要高效的D2D互连,以优化总拥有成本(TCO),包括面积效率、能源效率和延迟。

为了充分发挥异构集成的优势,需要深入了解最终应用和工作负载,以及如何为特定领域设计最佳解决方案。这涉及到从片上转向封装,将SoC网络在封装上传输,并为片上传输层添加物理层传输。

在芯片间传输数据的竞争协议中,AMBA CHI、UCIe和BoW最为知名。Arm的Dimond认为,chiplet互连将从现有的板载或SoC互连演化而来,但需要考虑更多层次。西门子的David Fritz指出,汽车设计中的分区特别具有挑战性,需要工具来探索复杂性并得出深层次的要求。

异构系统中的分区不仅涉及硬件,软件也需要跨芯片兼容。Eliyan的Kevin Donnelly提到,推理和训练对互连和带宽的需求不同,这影响了芯片组的分区。Patrick Soheili强调,将单片芯片上的组件分开时,需要考虑电力和通信速度,这影响了分区决策。

chiplet系统的出现带来了新的挑战,包括测试D2D接口以适应更高数据速率,以及集成来自不同供应商的D2D互连和芯片组。Alphawave的Giuliano提到,需要新的方法来测试D2D互连物理层,并与OSAT合作实施结构测试。Arteris的Stevens强调,系统发现是芯片中需要标准化的领域,而验证IP也是芯片的关键。

总体而言,没有一种D2D互连能够适合所有芯片分区和架构,了解目标KPI以选择正确的D2D链路和芯片分区配置至关重要。随着对芯片互连的了解加深,商业芯片市场的出现仍需时日,但汽车行业等正在推动这一趋势,看到了使用chiplet概念实现可扩展架构的好处。

原文和模型

【原文链接】 阅读原文 [ 4556字 | 19分钟 ]

【原文作者】 半导体行业观察

【摘要模型】 moonshot-v1-32k

【摘要评分】 ★★★★★