文章摘要

【关 键 词】 台积电、半导体、FinFET、GAA、BSPDN

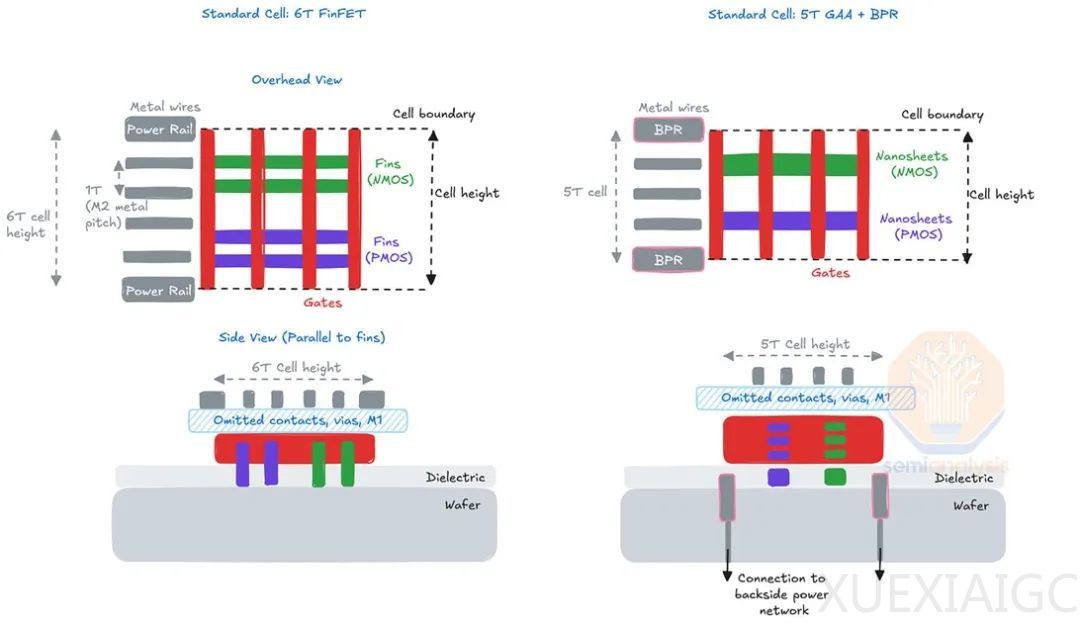

台积电在半导体制造领域继续保持其领先地位,尤其是在FinFET技术方面。目前,包括英特尔在内的所有重要前沿逻辑设计都在台积电的N5和N3工艺上生产,而竞争对手如三星和英特尔则在追赶。尽管台积电的未来地位尚未确定,但FinFET技术已接近极限,SRAM微缩在几个节点上停滞不前,行业正处于关键转折点。未来2-3年内,前沿逻辑必须采用全栅极(GAA)和背面供电(BSPDN)两种新范式。

英特尔在10nm节点上的失败导致其失去了三年的领先优势,部分原因是未能采用EUV技术以及在工具供应链不成熟的情况下过渡到钴金属化。GAA和BSPDN的新模式为代工厂的竞争秩序带来了新的机会,甚至可能为新进入者如日本政府支持的2nm代工初创公司Rapidus打开大门。

随着建造尖端晶圆厂所需的资本支出的增加,三星或英特尔可能被迫退出竞争。BSPDN技术通过将电源布线移至晶圆背面,为信号布线留出空间,从而改善了电力传输,减少了功率损耗,并减少了对积极互连微缩的需求。

目前,有三种不同的背面供电方法正在探索和/或实施:埋地电力轨(BPR)、PowerVia和直接背面接触(DBC)。每种方法都有其优势和挑战。例如,BPR简单但存在污染风险,PowerVia避免了污染风险并提供了更好的电池尺寸缩小效果,而DBC提供了最大的扩展优势,但生产难度最高。

在代工厂路线图上,GAA和BSPDN在时间和架构上存在显著差异。Rapidus计划在2025年开设一条2nm试验线,并在2027年实现大批量生产。三星在2022年率先在SF3E节点上量产GAA,但产品化程度有限。英特尔正在加速其GAA + BSPDN节点18A,而台积电则稳步推进其N2节点,计划在2026年推出首个GAA + 背面电源节点A16。

SRAM微缩是推动芯片功能逐代改进的关键因素,但自5nm节点以来,SRAM位单元微缩一直停滞不前。GAA晶体管可能在从finFET到GAA的转变中提供一次性的缩小优势,但在后续节点中可能不会有太大优势。SRAM外围设备仍受益于现代DTCO和其他扩展技术,但在关键应用中,外围设备仅占SRAM总面积的一小部分,因此好处不会那么明显。

总体而言,三大代工厂将在2025年真正大规模推出GAA,Rapidus将在2027年紧随其后。英特尔将率先推出BSPDN,时间比预期早一年左右,但尽管名为18A,但其密度更接近3纳米工艺。

原文和模型

【原文链接】 阅读原文 [ 5603字 | 23分钟 ]

【原文作者】 半导体行业观察

【摘要模型】 moonshot-v1-32k

【摘要评分】 ★★★★★