文章摘要

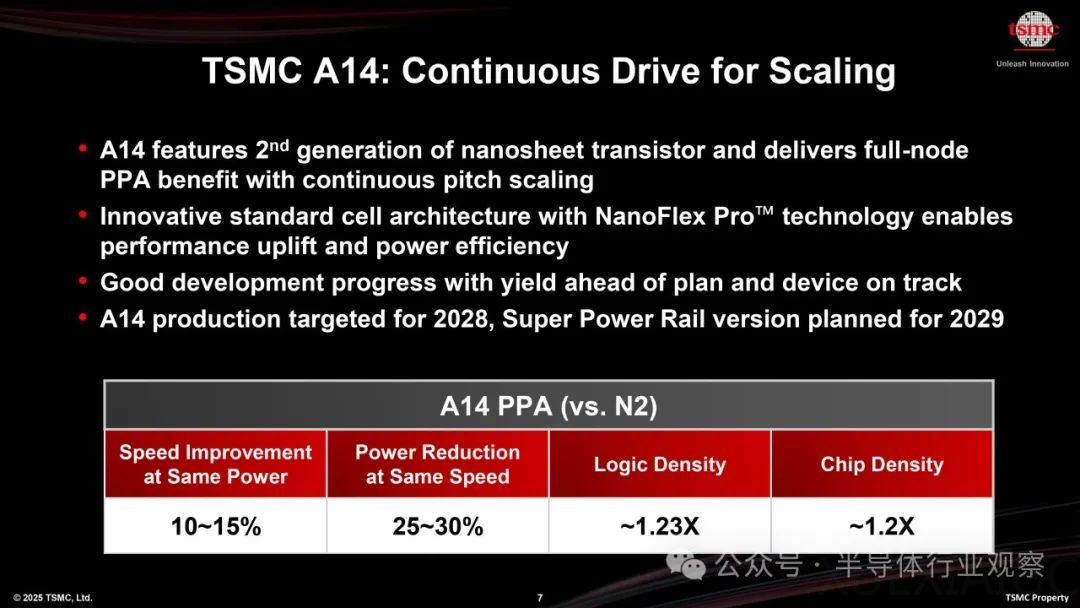

台积电在TSMC Symposium 2025上发布了一系列新技术,并更新了其技术路线图,展示了其在半导体领域的持续创新。第二代GAA工艺14A首次曝光,计划于2028年投产,预计在相同功耗下速度提升15%,或在相同速度下功耗降低30%,逻辑密度提升20%以上。该工艺旨在推动人工智能(AI)转型,并通过提升智能手机的内置AI功能,使其更加智能。台积电凭借其在纳米片晶体管设计与技术协同优化方面的经验,正在将其TSMC NanoFlex标准单元架构升级为NanoFlex Pro,以实现更高的性能、能效和设计灵活性。

除了A14,台积电还推出了新的逻辑、特殊工艺、先进封装和3D芯片堆叠技术,这些技术为高性能计算(HPC)、智能手机、汽车和物联网(IoT)等广泛的技术平台做出了贡献。台积电持续推进其晶圆上芯片基板 (CoWoS) 技术,计划于2027年实现9.5 reticle size CoWoS的量产,将12个或更多HBM堆栈与台积电领先的逻辑技术集成在一个封装中。此外,台积电还推出了基于CoWoS的产品SoW-X,旨在创建一个晶圆大小的系统,其计算能力是现有CoWoS解决方案的40倍。

在手机领域,台积电利用其最新一代射频技术N4C RF,支持边缘设备上的人工智能及其对高速、低延迟无线连接的需求。与N6RF+相比,N4C RF的功耗和面积减少了30%,计划于2026年第一季度投入风险生产。在汽车领域,台积电以最先进的N3A工艺满足高级驾驶辅助系统(ADAS)和自动驾驶汽车(AV)对计算能力的严苛要求,该工艺已通过AEC-Q100一级认证的最终阶段,并持续改进缺陷,以满足汽车百万分率(DPPM)的要求。

在物联网领域,台积电此前宣布的超低功耗N6e工艺现已投入生产,该公司正瞄准N4e工艺,继续突破未来边缘人工智能的能效极限。台积电的A14是一种全新的制程技术,基于该公司的第二代GAAFET纳米片晶体管和新的标准单元架构,以实现性能、功耗和微缩优势。台积电预计,与N2相比,A14将在相同的功耗和复杂度下实现10%至15%的性能提升,在相同的频率和晶体管数量下降低25%至30%的功耗,并在混合芯片设计和逻辑电路中提高20%至23%的晶体管密度。

台积电的3nm技术也取得了显著进展。N3P已投入生产,N3X进展顺利,预计将在相同功率下将最大性能提高5%,或在相同频率下将功耗降低7%。台积电的封装技术也在不断演进,3DFabric技术组合为客户提供了完整的产品级解决方案,涵盖了堆叠或芯片级/晶圆级集成的选项。台积电的先进封装技术已远远超越了2.5D中介层技术,未来先进制程和先进封装需要协同发展,才能实现即将出现的产品创新。

台积电的技术领导力和卓越的制造能力为其客户提供了可靠的创新路线图,推动人工智能的未来发展。台积电的尖端逻辑技术(例如A14)是连接物理世界和数字世界的全面解决方案的一部分,旨在释放客户的创新潜能。随着人工智能正以惊人的速度消耗着尖端硅片,台积电凭借多年来为智能手机和其他电池供电设备制造移动SoC的优势,占据了非常有利的地位。

原文和模型

【原文链接】 阅读原文 [ 4941字 | 20分钟 ]

【原文作者】 半导体行业观察

【摘要模型】 deepseek/deepseek-v3/community

【摘要评分】 ★★★★★