文章摘要

【关 键 词】 硅基二维、异质集成、eDRAM技术、数据存储、性能提升

复旦大学微电子学院的周鹏教授、包文中研究员和信息科学与工程学院的万景研究员合作,研发了一种创新的“硅基-二维”异质集成eDRAM(Si-MoS₂ eDRAM)技术。这项技术结合了二维半导体沟道的超低泄露电流优势和成熟的硅基SOI工艺,突破了传统增益单元eDRAM存储时间短的瓶颈,并通过三维异质叠层工艺实现了集成密度的显著提升。研究成果发表在Nature Communications期刊上,引起了广泛关注。

现代计算机架构中,缓存内存容量不断增大,以缩小处理单元与主存储器之间的性能差距。传统6T-SRAM缓存集成密度低且功耗高,而1T1C eDRAM虽集成密度高,但存在电荷共享操作和对额外电容的需求限制了电压缩放。增益单元eDRAM(GC-eDRAM)作为一种新的结构选择,结合了两到四个晶体管以实现读取、写入和随机访问功能,但其数据直接存储在存储晶体管的栅极电容中,随着晶体管尺寸缩小,存储电容减少,同时写入晶体管的关断电流增加,显著降低了数据保持时间。

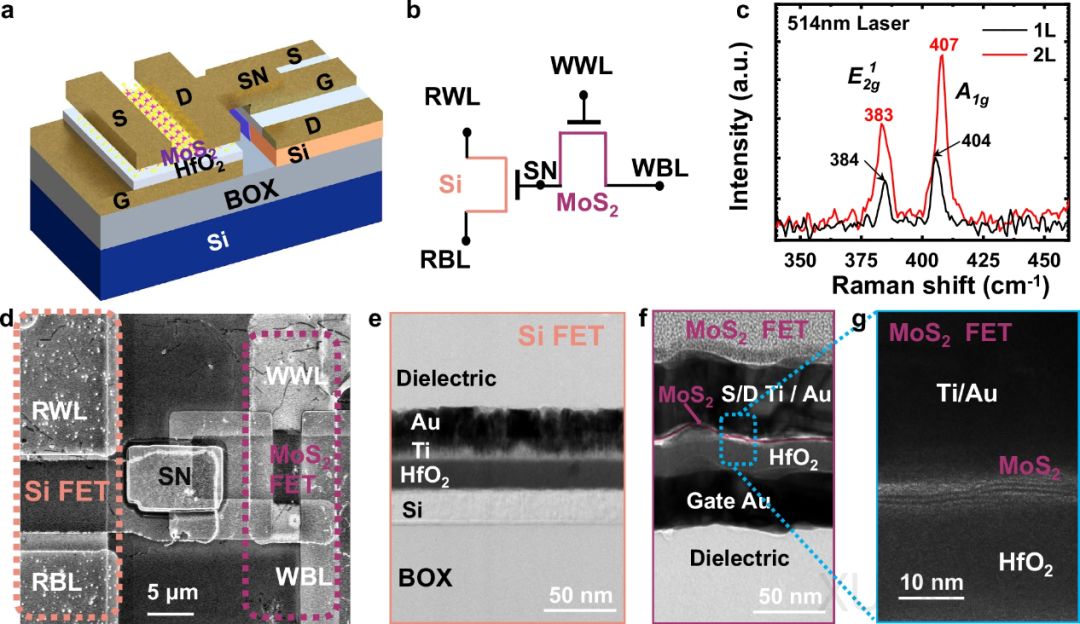

为了解决这些问题,复旦大学团队提出了一种融合成熟硅基工艺和新型二维原子晶体MoS₂的GC-eDRAM结构,以克服数据保持时间短的问题,并进一步提高GC-eDRAM的集成密度。MoS₂具有原子级厚度、适中的带隙、超低关态电流以及日益成熟的晶圆级材料生长技术。通过后端工艺将晶圆级MoS₂可控转移到硅晶圆上进行集成,成功将三个原子级厚度的二维半导体MoS₂集成到硅SOI电路中,开发了一种由两晶体管组成的异质GC-eDRAM(2T-eDRAM)结构,其中MoS₂被用作写入晶体管的沟道材料,并表现出接近理论极限的亚阈值斜率。

异质Si-MoS₂ eDRAM的数据显示保持时间可达6000秒,感应裕度高达35 μA/μm,与同时制造的纯Si和纯MoS₂ eDRAM相比,分别提高了1000倍和100倍。此外,该器件的访问时间可降至5纳秒,完全满足高层缓存应用的需求。而通过CMOS兼容的BEOL工艺也成功演示了3D堆叠结构的Si-MoS₂ eDRAM,其集成密度大幅提高。

这项研究成果展示了令人振奋的超长保持时间、高感应裕度、快速访问速度、CMOS兼容性和高集成密度的多方面优势,未来极具工程应用潜力和价值,也有望革新大容量缓存技术,从而突破现代高性能计算机系统的瓶颈。

原文和模型

【原文链接】 阅读原文 [ 3608字 | 15分钟 ]

【原文作者】 半导体行业观察

【摘要模型】 moonshot-v1-32k

【摘要评分】 ★★★★★