文章摘要

【关 键 词】 半导体、工艺技术、晶体管、芯片封装、技术突破

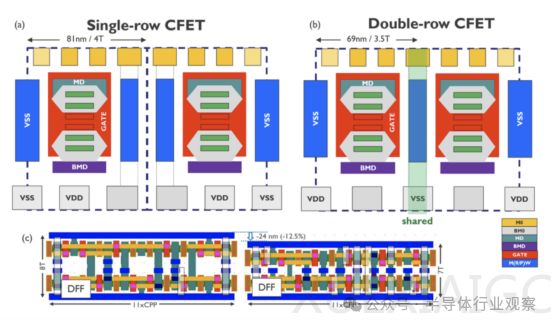

全球半导体行业正积极推进工艺技术,英特尔、台积电和三星等公司正将工艺推进至1.8nm(18A)和1.6nm(16A),采用全栅极晶体管技术。imec研究下一代互补场效应晶体管(CFET)堆叠晶体管技术,并计划在2024年IEEE国际电子设备会议(IEDM)上展示其CFET标准单元。该标准单元包含两行CFET,中间有一个共享信号布线墙,与传统单行CFET相比,新架构简化了工艺并显著减少了逻辑和SRAM单元面积。

imec的双行CFET架构允许将标准单元高度从4T降低到3.5T,显著减少SRAM单元面积。该架构从基单元开始,一侧针对电源连接优化,另一侧针对信号连接优化,通过中间布线壁(MRW)实现上下连接。imec的DTCO研究表明,每3.7个FET共享一个MRW足以构建逻辑和SRAM单元,与单行CFET相比,这种新架构进一步降低了标准单元高度,减少了SRAM单元面积。

英特尔在IEDM上宣布了在二维晶体管技术方面的技术突破,包括超硅材料、芯片互连和封装技术。英特尔展示了提高全栅(GAA)晶体管规模和性能的新研究,包括使用硅和超硅材料的原子级厚度2D晶体管。英特尔还概述了其减法钌技术,提高互连性能和可扩展性,以及芯片封装突破,提高芯片到芯片的组装吞吐量。

英特尔的RibbonFET是FinFET问世13年以来的首款新型晶体管设计,采用堆叠的纳米片,完全被栅极包围。英特尔正在通过标准硅设计和使用新的2D材料进一步缩小GAA设计。英特尔使用钼基材料制造了栅极长度为30nm的2D全栅极NMOS和PMOS晶体管,实现了“同类最佳的NMOS驱动电流”。

英特尔的新选择层转移(SLT)技术能够以极高速度将整个芯片晶圆连接到另一个晶圆上,提高芯片到芯片组装过程的吞吐量。SLT技术使用无机红外激光脱键合,使超薄芯片具有更好的灵活性,实现更小的芯片尺寸和更高的纵横比。英特尔还将在IEDM上就未来的封装解决方案发表演讲,展示EMIB-T技术,这是首个使用TSV通过桥接器发送信号的EMIB实现。

原文和模型

【原文链接】 阅读原文 [ 3400字 | 14分钟 ]

【原文作者】 半导体行业观察

【摘要模型】 moonshot-v1-32k

【摘要评分】 ★★★★★