文章摘要

【关 键 词】 半导体封装、微型芯片、集成密度、高性能计算、技术挑战

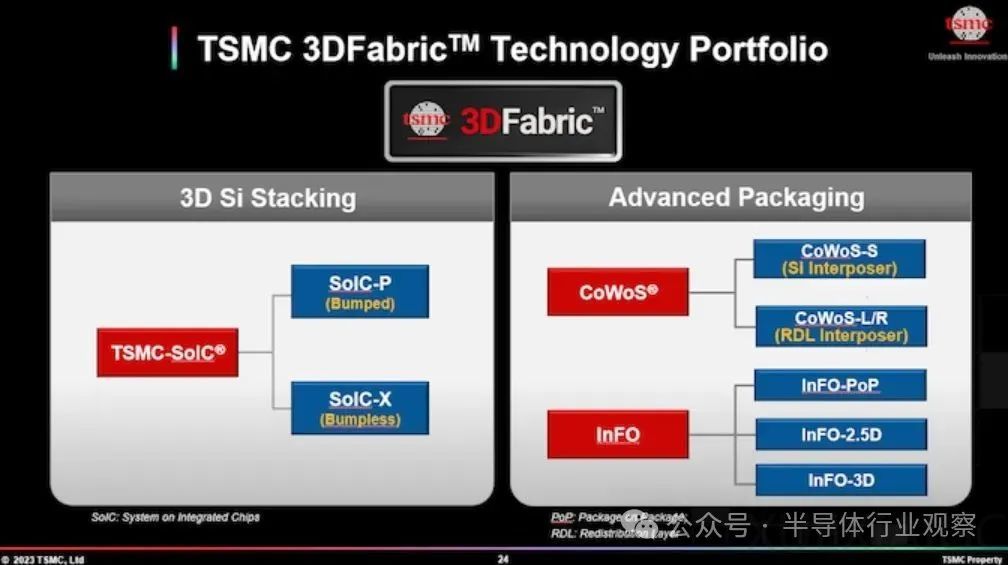

在半导体封装领域,技术的快速进步正推动着微型芯片的集成密度和工作性能的提升。传统的二维(2D)封装技术正逐渐被更先进的二维点五(2.5D)和三维(3D)封装技术所取代。2.5D封装通过精细布线的中介层,缩小了芯片之间的间距,增强了信号传输带宽,而3D封装则通过垂直堆叠芯片,大幅减少安装面积,进一步提高了密度。

近期,一种称为“3.5维(3.5D)”的封装技术亮相,它结合了2.5D和3D封装的优点,进一步提升了集成密度和操作性能。AMD在其最新GPU产品“MI300系列”中采用了3.5D封装技术,通过硅中介层大幅增加了传输通道数量,提高了性能。英特尔也在开发3.5D封装技术,并在ECTC 2024上展示了其研究成果,包括3μm间距的HBI技术,这标志着向更高密度封装的重大进展。

此外,台积电的3D堆叠SoIC技术计划在2027年前将凸块间距缩小至3μm,这将使得芯片之间的连接数量大幅增加,从而显著提升芯片的带宽密度。这种技术的进步对于构建大型、超密集的分解式处理器设计尤为重要,能满足高性能计算(HPC)客户对面积和性能的严苛要求。

这些先进封装技术的发展不仅提高了半导体器件的性能,也带来了技术上的挑战。混合键合作为连接技术之一,虽然被看作是提高硅芯片之间连接密度的最有前途的方法,但其技术难度不容小觑。不过,可以预见的是,随着技术的不断成熟,未来半导体封装将实现更高的集成度,为电子产品带来革命性的改进。

原文和模型

【原文链接】 阅读原文 [ 3449字 | 14分钟 ]

【原文作者】 半导体行业观察

【摘要模型】 glm-4

【摘要评分】 ★★★★★

© 版权声明

文章版权归作者所有,未经允许请勿转载。

相关文章

暂无评论...