文章摘要

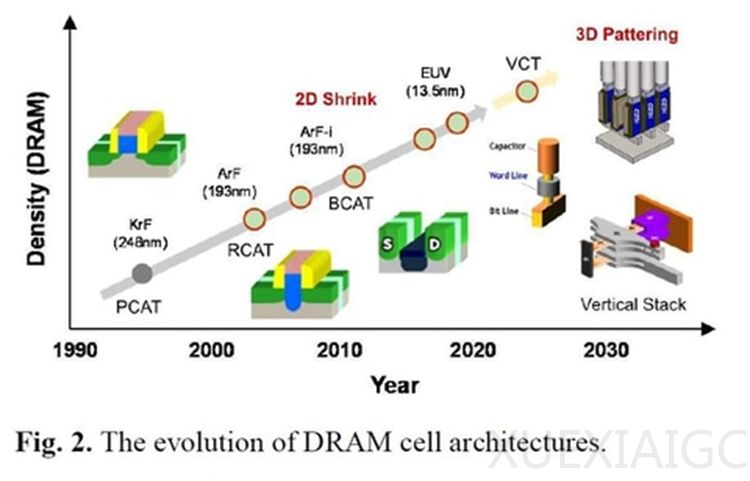

三星电子在“IMW 2025”会议上详细介绍了下一代DRAM和NAND闪存的技术演变。在DRAM部分,三星回顾了DRAM单元从1990年代至今的发展历程。早期的平面n沟道MOS FET逐渐被垂直沟道晶体管(VCT)取代,以应对短沟道效应和关断漏电流问题。2010年代,DRAM单元布局从“8F2”改进为“6F2”,显著减少了单元面积。随着光刻技术的进步,DRAM单元面积不断缩小,10nm代DRAM延续了七代,分别称为“1X→1Y→1Z→1A→1B→1C→1D”代。下一代“0A”代DRAM有望转向“4F2”布局,采用垂直沟道晶体管结构,进一步提升内存密度。此外,三维DRAM(3D DRAM)通过垂直堆叠单元阵列,进一步增加了内存容量。

在NAND闪存部分,三星介绍了从平面NAND到3D NAND的演变。平面NAND在2010年代初达到小型化极限,3D NAND通过将单元串从水平方向转换为垂直方向,显著增加了单元可存储的电荷量,并减少了相邻单元之间的干扰。3D NAND还实现了多值存储,即在一个单元中存储三位数据。2010年代初期的3D NAND产品有32层,到2020年代中期已发展到300多层,高度约为其原始高度的十倍。然而,随着堆叠层数的增加,3D NAND也面临蚀刻难度增加、相邻单元干扰加剧等挑战。为解决这些问题,三星尝试使用铁电膜替代传统的氮氧化物(ONO)膜,以降低编程电压和抑制阈值电压波动,进一步支持多值存储。

三星在主题演讲中强调了DRAM和NAND闪存面临的诸多技术挑战,并提出了可能的解决方案。全球企业和专家也在会议上分享了各自的技术进展,如imec的纯金属栅极技术、铠侠的多级编码技术、应用材料公司的快速外延生长技术等。这些创新为DRAM和NAND闪存的未来发展提供了新的可能性。尽管技术挑战依然存在,但通过持续的研发和创新,DRAM和NAND闪存有望继续推动半导体行业的进步。

原文和模型

【原文链接】 阅读原文 [ 2468字 | 10分钟 ]

【原文作者】 半导体行业观察

【摘要模型】 deepseek-v3

【摘要评分】 ★★★☆☆