文章摘要

【关 键 词】 台积电、3D堆叠、SoIC技术、先进封装、高性能计算

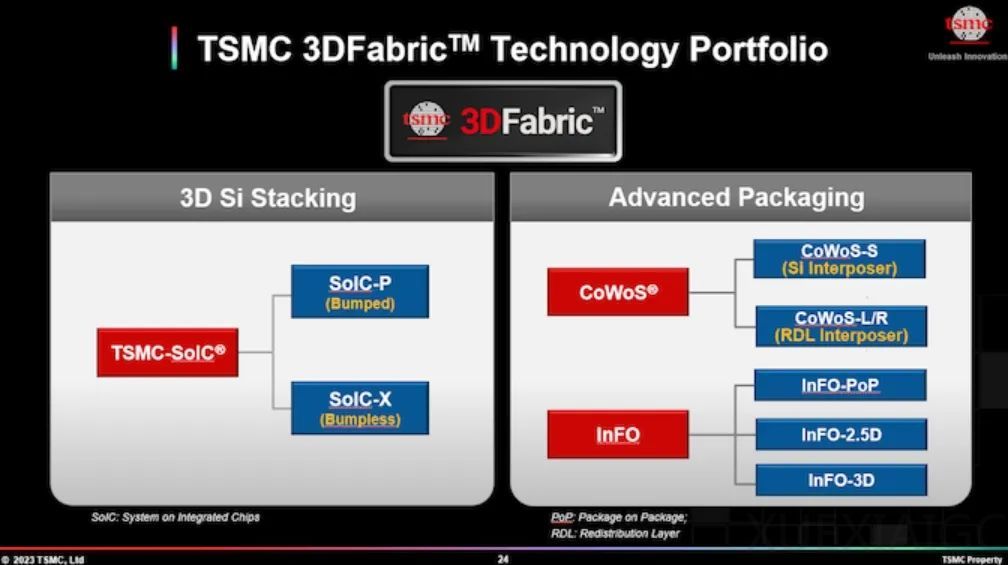

台积电的3D堆叠系统级集成芯片(SoIC)先进封装技术预计将迅速发展。该技术涉及将两个先进的逻辑器件直接堆叠,通过超密集的连接来提升高性能部件的表现。

到2027年,台积电计划将SoIC技术的凸块间距从现有的9μm缩小至3μm,使得能够将1.6纳米级的A16芯片与2纳米级的N2芯片通过3μm键合间距的硅通孔(TSV)连接,提升组装芯片的带宽密度。

此外,台积电还计划推出针对低成本、低性能应用的凸块SoIC-P封装工艺。到2025年,将提供能将0.2光罩大小的N3顶部芯片与N4底部芯片配对的正面对背面(F2B)凸块技术,使用25μm间距微凸块进行连接。

2027年,将推出正面对背面(F2F)凸块技术,实现N2顶部芯片与N3底部芯片的16μm间距堆叠。

台积电对SoIC技术的行业采用持乐观态度,预计到2026年至2027年间将推出约30种SoIC设计。为了让SoIC更受芯片开发商欢迎,台积电还需持续改进芯片到芯片的接口技术。

通过这些技术进步,台积电期望为不同性能需求和应用成本提供多元化的封装解决方案,进一步巩固其市场领导地位。

原文和模型

【原文链接】 阅读原文 [ 1114字 | 5分钟 ]

【原文作者】 半导体行业观察

【摘要模型】 glm-4

【摘要评分】 ★★☆☆☆

© 版权声明

文章版权归作者所有,未经允许请勿转载。

相关文章

暂无评论...