文章摘要

近年来,人工智能的快速发展推动了GPU市场的繁荣,而台积电的CoWoS封装技术在这一过程中扮演了关键角色。作为英伟达的重要合作伙伴,台积电在AI领域的合作进一步深化,尤其是在CoWoS封装技术方面。英伟达首席执行官黄仁勋明确表示,台积电的CoWoS技术是目前唯一的选择,尤其是在Blackwell系列产品中,CoWoS-L封装将成为主流。这一技术不仅为台积电带来了丰厚的收入,还使其超越日月光,成为全球最大的封测厂商。

CoWoS技术的演进面临多重挑战。随着芯片尺寸的不断增大,例如AI芯片尺寸可能达到80×84毫米,一块12英寸晶圆只能容纳四个这样的芯片。超大尺寸的CoWoS封装在基板尺寸和散热方面面临严峻挑战。例如,5.5倍光罩版本需要100×100毫米的基板,而9倍光罩版本则超过120×120毫米。这些大尺寸基板对系统设计和数据中心配置提出了更高的要求,尤其是在电源和冷却系统方面。此外,CoWoS封装中使用的助焊剂也带来了新的问题。随着中介层尺寸的增大,助焊剂的清除变得更加困难,残留的助焊剂可能影响芯片的可靠性。

台积电正在积极应对这些挑战。针对助焊剂问题,台积电正在探索无助焊剂键合技术的应用,并计划在2023年底完成测试。在中介层尺寸方面,台积电计划到2026年推出具有5.5倍掩模尺寸的CoWoS-L,并在2027年推出具有9.5倍掩模尺寸的CoWoS。此外,台积电还在开发SoW-X技术,该技术模拟了完整的服务器机架功能,计划于2027年实现量产。

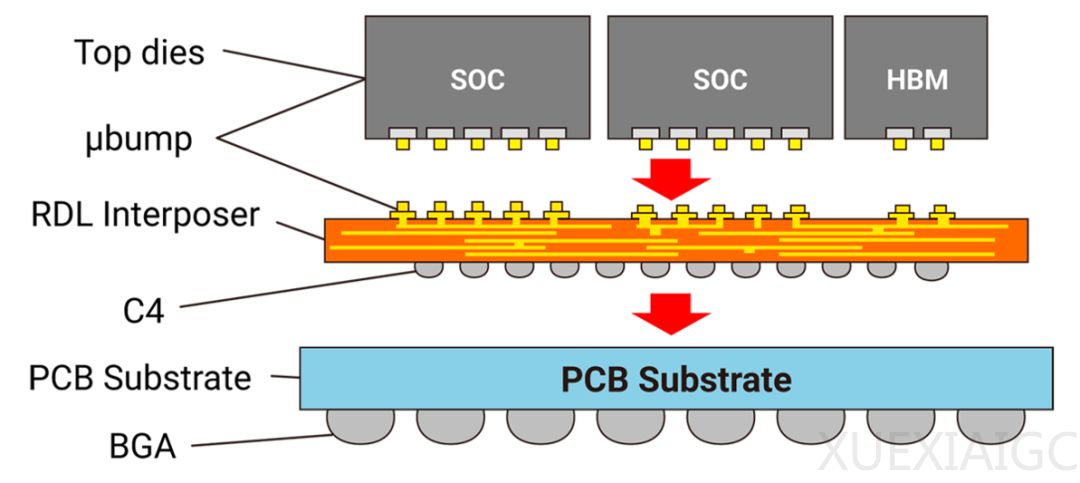

FOPLP和CoPoS技术的出现为封装行业带来了新的可能性。FOPLP(扇出型面板级封装)和CoPoS(基板上面板芯片封装)均采用大型面板基板进行封装,但两者在架构和应用方面存在显著差异。FOPLP无需中介层,适用于边缘AI和移动设备等应用,而CoPoS则采用中介层,更适合高端AI和HPC系统。台积电计划于2029年实现CoPoS技术的量产,并有望将英伟达作为其首个客户。

CoPoS技术的优势在于其方形面板设计。与传统圆形晶圆相比,矩形基板提供了更大的可用空间,从而提高了产出效率并降低了成本。此外,CoPoS中的中介层材料正在从传统的硅演变为玻璃,提供了更高的成本效益和热稳定性。玻璃芯基板具有更高的互连密度、更灵活的信号布线、更少的RDL层数、更高的带宽密度以及更低的单次数据传输功耗。

尽管CoPoS技术前景广阔,但其普及仍面临诸多挑战。从圆形封装工艺到方形封装工艺的转变需要大量的材料和设备研发投入。此外,高精细导体图案的实现需要克服翘曲、均匀度等问题,这对良率提出了更高的要求。客户对RDL线宽/间距的要求从10µm缩小到5µm,甚至2µm、1µm,这需要供应商在RDL布局方面实现新的突破。

总体而言,台积电在封装技术领域的持续创新为其在AI和高性能计算市场中的领先地位提供了有力支持。然而,未来技术的普及和商业化仍需克服诸多技术难题。

原文和模型

【原文链接】 阅读原文 [ 2567字 | 11分钟 ]

【原文作者】 半导体行业观察

【摘要模型】 deepseek-v3

【摘要评分】 ★★★★★