文章摘要

【关 键 词】 封装市场、3D堆栈、半导体、异构集成、技术革新

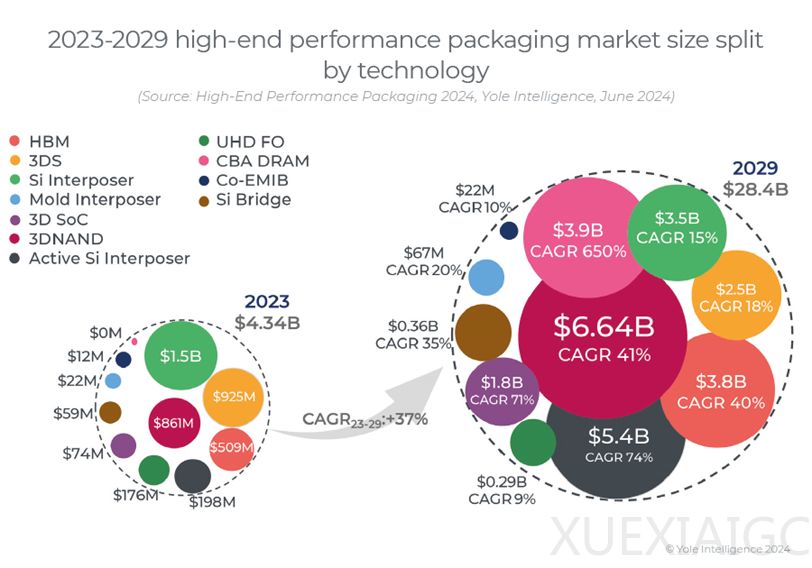

根据Yole的分析,2023年全球先进封装市场价值为43亿美元,预计到2029年将达到280亿美元,复合年增长率为37%。电信和基础设施是最大的市场,占2023年收入的67%以上,而移动和消费者市场增长最快,复合年增长率为50%。在封装单位方面,预计2023-2029年将实现44%的复合年增长率,从6.27亿个单位增至56亿个单位。这主要得益于2.5D和3D平台推动价值从前端到后端的转变,以及先进封装相较于传统封装更高的平均售价。

3D堆栈内存(包括HBM、3DS、3D NAND和CBA DRAM)将是市场增长的主要驱动力,到2029年将占据超过70%的市场份额。其中,CBA DRAM、3D SoC、有源硅中介层、3D NAND堆栈和嵌入式硅桥等平台的增长速度最快。

在半导体供应链中,先进封装正在引发一场颠覆性变革。代工厂、IDM和OSAT在高端封装市场展开激烈竞争,使得小型企业面临更大的竞争压力。随着混合键合等技术的采用,高端封装供应链的进入门槛不断提高,主要参与者凭借前端能力在先进封装领域占据优势。

台积电、英特尔和三星等领先企业通过CoWoS、InFO、3D SoIC、Foveros、EMIB等解决方案,展示了其在3D集成和异构封装领域的技术实力。这些企业不仅在开发、生产和投资方面表现突出,还在知识产权申请方面占据领先地位。例如,台积电为特斯拉和Cerebras提供InFO_SoW解决方案,英特尔的Lakefield Foveros封装销往三星、微软和联想等客户,三星电子则是HBM内存3D TSV堆叠技术的先驱。

随着摩尔定律接近极限,封装技术成为推动半导体行业创新的关键支柱。为了应对数字终端系统的需求和技术创新,行业正转向采用2.5D和3D异构集成技术,以实现更高的互连密度、带宽和功率效率。SoC分区和”小芯片”集成被认为是一种潜在的发展方向,通过优化扩展成本来实现系统级扩展。

在技术细分方面,UHD FO、2.5D中介层、3D堆叠存储器和嵌入式硅桥等关键技术正推动市场份额的增长。这些技术可以组合和共存,以满足未来的需求,如英特尔的Co-EMIB和台积电的InFO_LSI。未来一代封装解决方案将实现系统级密度更高的3D IC,间距≤10μm,混合键合技术将成为关键。

总体来看,先进封装技术正朝着减小互连间距、降低通孔直径和晶圆厚度的方向发展,以实现更复杂的单片芯片集成和更快的数据处理传输。预计未来将在同一封装中结合更多2.5D和3D平台,如3D SoC、2.5D中介层、嵌入式硅桥和MTV共封装光学器件集成芯片等,使高端封装变得更加复杂。

原文和模型

【原文链接】 阅读原文 [ 1882字 | 8分钟 ]

【原文作者】 半导体行业观察

【摘要模型】 moonshot-v1-32k

【摘要评分】 ★★★★☆