文章摘要

通过采用三维堆叠计算架构,研究人员开发了一种用于3D集成芯片的新型电源技术。这一技术将处理单元直接放置在动态随机存取存储器(DRAM)堆栈上方,显著提升了芯片的性能和效率。为了实现这一目标,研究团队开发了精密高速键合技术和新型粘合剂技术,这些技术不仅满足了高性能计算应用对高内存带宽的需求,还实现了低功耗和低电源噪声。

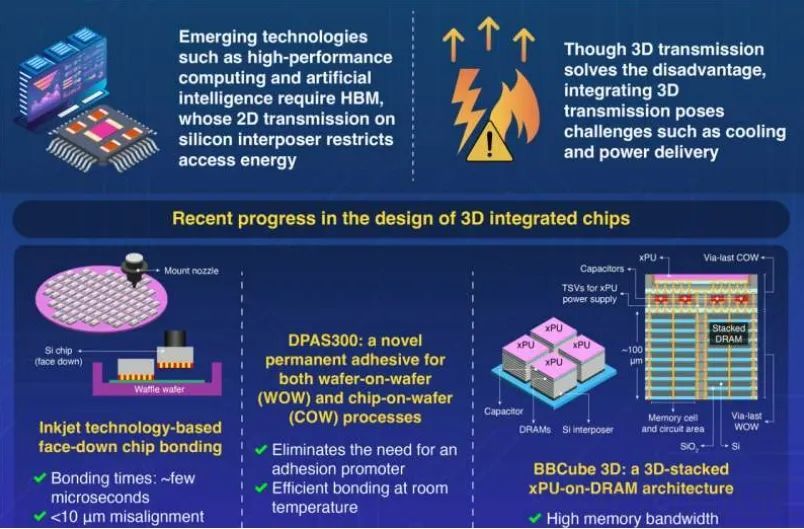

传统的系统级封装(SiP)方法在二维平面上排列半导体芯片,但其尺寸受限,无法满足现代高性能计算的需求。为此,日本东京科学研究所的研究团队提出了一种名为BBCube的创新型2.5D/3D芯片集成方法。BBCube通过面朝下的晶圆上芯片(COW)工艺,成功规避了传统焊料互连的局限性。研究团队利用喷墨技术和选择性粘合剂涂覆方法,将不同尺寸的芯片顺序键合到300毫米华夫晶圆上,芯片间间距仅为10微米,最短贴装时间不到10毫秒。

在COW工艺中,超过30,000个不同尺寸的芯片被制造到华夫晶圆上,实现了更快的键合速度,并且没有发生任何芯片脱落故障。为了确保超薄晶圆多层堆叠的热稳定性,研究人员开发了一种新型粘合剂材料DPAS300。这种由有机-无机混合结构组成的粘合剂在实验研究中表现出了良好的粘合性和耐热性,适用于COW和晶圆对晶圆工艺。

为了进一步提升BBCube的性能,研究团队采用了3D xPU-on-DRAM架构,并通过新的电源分配高速公路进行强化。这一架构在xPU和DRAM之间嵌入电容器,在华夫晶圆上实现重新分布层,并在晶圆通道和DRAM划线中放置硅通孔。这些创新不仅将数据传输所需的能量降低到传统系统的五分之一到二十分之一,还将电源噪声抑制到50毫伏以下。

东京科学研究所的研究成果在2025 IEEE第75届电子元件和技术会议(ECTC)上进行了展示,展示了其在下一代计算架构中的潜力。这些创新技术有望推动高性能计算的发展,为人工智能和其他计算密集型应用提供更高效、更可靠的解决方案。

原文和模型

【原文链接】 阅读原文 [ 945字 | 4分钟 ]

【原文作者】 半导体行业观察

【摘要模型】 deepseek-v3

【摘要评分】 ★★☆☆☆