文章摘要

飞利浦半导体公司(现为恩智浦半导体公司)于1980年发明的I2C总线,在简化嵌入式系统通信方面迈出了重要一步。作为一种简单的双线接口,I2C用于同步、多主/多从、单端串行通信,至今仍广泛用于连接低速外设集成电路、处理器和微控制器。然而,随着技术的发展,硅片已经从8位MCU发展到多核SOC,从简单的传感器发展到复杂的多模传感器设备,对带宽、延迟和功耗的需求也在不断增加。这为新型改进型总线变体的发展提供了契机。

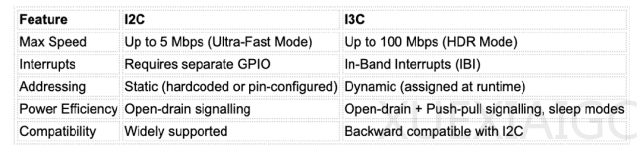

I3C(Improved Inter-Integrated Circuit)是由MIPI联盟开发的一种总线,基于I2C的双线接口,并对其进行了改进以提高速度和效率。它旨在取代I2C(以及部分SPI),同时仍保持与I2C的向后兼容。I3C提供高达12.5 MHz的更高时钟速度、无需额外线路的带内中断、动态寻址、双数据速率和多通道操作(最高可达100Mbps)、节能模式以及标准化命令集。它是专为现代嵌入式系统打造的更快、更精简的继任者,并正迅速成为SoC和FPGA设计人员的默认选择。

I2C的成功得益于其简单的一条数据线(SDA)和一条时钟线(SCL)以及主/从架构,总线上最多可连接127个设备。它不需要像SPI那样每个设备都进行片选,这使其成为低引脚数封装和简化电路板布线的理想选择。然而,随着SOC变得越来越复杂,时间敏感的设计人员开始达到I2C的极限。尽管I2C经历了多次迭代,包括400 kbit/s快速模式、1 Mbit/s加快速模式、3.4 Mbit/s高速模式和5 Mbit/s超快速模式,但其线路速率仍不足以满足当今对高速传感器或复杂外设日益增长的需求。

I3C由MIPI联盟开发,旨在解决这些限制,同时仍保持与传统I2C设备的向后兼容性。I3C相对于I2C有很多关键优势,其中最重要的是更高的吞吐量。在SDR(单数据速率)模式下,其时钟频率高达12.5MHz,即使在广泛采用的快速模式下,其速度也比I2C快10倍,是I2C顶级超快速模式的两倍多。此外,I3C还可以在HDR(高数据速率)模式下运行,将性能进一步推高至100 Mbps。I3C的动态寻址允许在总线初始化期间分配设备地址,这与I2C硬编码或引脚可配置地址不同,简化了PCB设计并实现了更具可扩展性的系统。带内中断(IBI)的加入消除了对外部中断线的需求,并允许目标设备通过同一双线接口发出中断以响应控制器活动,这使得I3C成为事件驱动架构的理想选择。多种节能功能使其能够实现更高的能效。热连接允许设备在总线运行时动态加入总线,设备可以高效地进入睡眠状态并被唤醒。此外,与I2C仅支持开漏操作不同,推挽信号传输的加入进一步降低了功耗。

在评估项目的I3C IP核时,需注意以下几点:符合最新的MIPI I3C规范(v1.1.1或v1.2);向下兼容以实现无缝I2C回退(这对于混合环境至关重要);可配置的角色(包括辅助主设备的动态角色切换);支持HDR,以便在传输大数据块时充分利用更高的数据速率(HDR-DDR、HDR-TSP/TSL、HDR-BT)。向I3C的过渡可能是一个循序渐进的过程,尤其是在使用传统设备的系统中。以下几个指标表明是时候进行迁移了:可能需要更高的带宽;中断所需的GPIO线路过多;设计对功耗敏感;或者需要一个面向未来的协议来降低延迟和电路板复杂性。

与80年代相比,如今的嵌入式系统速度更快、更复杂,功耗感知也更强。数十年来,I2C一直是系统设计中不可或缺的接口,并经历了多次迭代。I3C正是为应对新挑战而生,它不仅保留了我们熟悉的两线式简洁性,还兼具现代系统所需的性能。如果正在构建下一个ASIC或为FPGA设计选择外设,I3C是一个很好的选择,它不仅是一种更快的总线,而且是芯片间通信的绝佳基础。

原文和模型

【原文链接】 阅读原文 [ 1394字 | 6分钟 ]

【原文作者】 半导体行业观察

【摘要模型】 deepseek-v3

【摘要评分】 ★★★☆☆