文章摘要

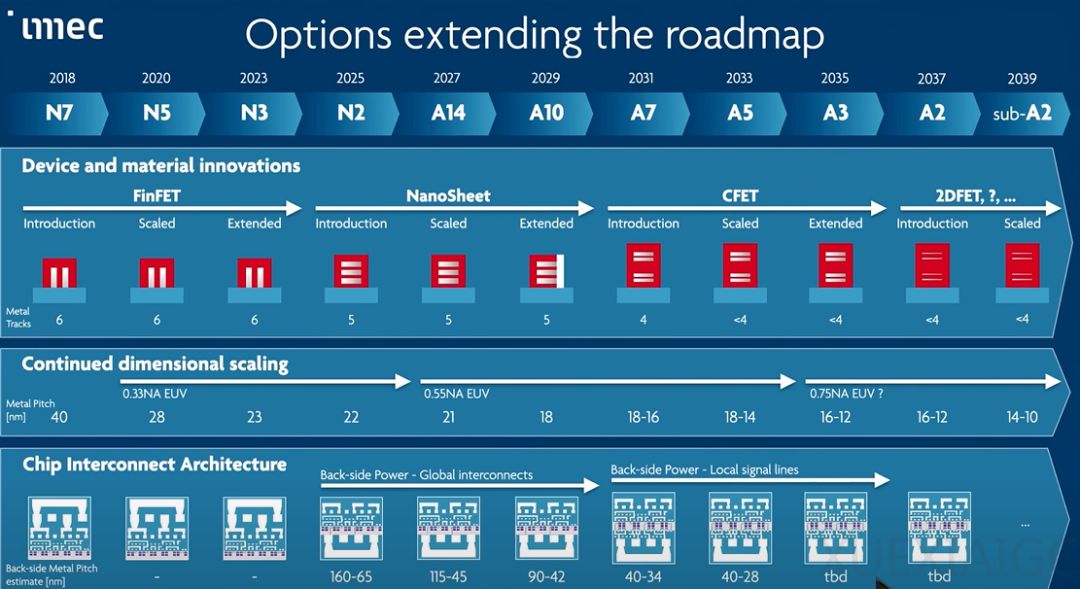

IMEC(比利时微电子研究中心)近期发布了直至2039年的半导体工艺路线图,详细预测了未来14年内半导体技术的发展趋势。作为全球半导体研发的核心机构,IMEC的路线图不仅展示了其对行业趋势的深刻洞察,还为全球半导体企业与科研机构提供了重要的参考方向。路线图涵盖了芯片工艺节点、晶体管架构、光刻技术、背面供电技术以及2D材料等多个关键领域,揭示了半导体行业从“尺寸微缩”到“架构革新”的范式转变。

首先,路线图对芯片工艺节点的命名方式进行了深入解读。当前,7纳米、5纳米、3纳米等工艺节点已成为先进处理器的主流技术,但这些数字已不再直接对应物理尺寸,而是成为衡量技术先进性的符号。随着FinFET(鳍式场效应晶体管)技术的普及,芯片性能的提升更多依赖于架构创新与密度优化,而非单纯的物理尺寸缩小。IMEC预测,随着工艺节点向2纳米及以下演进,FinFET架构将逐渐被NanoSheet(纳米片)晶体管架构取代。NanoSheet采用环绕闸极(GAA)结构,能够有效抑制量子隧穿效应带来的漏电流问题,为芯片性能提升与制程微缩提供了新的方向。

在光刻技术方面,IMEC指出,随着工艺节点向更先进的A14(1.4纳米)节点推进,High NA EUV(0.55 NA)光刻技术将逐步取代标准EUV(0.33 NA)技术。High NA EUV通过更高的光收集效率与更短的焦深控制,解决了标准EUV在极小节距下面临的线宽粗糙度与重叠误差问题,为纳米片架构所需的原子级精度图案转移提供了支持。未来,Hyper NA EUV(0.75 NA)技术有望成为CFET(互补场效应晶体管)时代的主流光刻技术,进一步推动半导体制造工艺进入“原子级操控”时代。

背面供电技术也是IMEC路线图中的重要创新之一。传统晶体管设计中,电源与数据信号通过平面线路传输,线路间的串扰问题制约了芯片性能。背面供电技术将电源传输路径转移至芯片背面,通过三维立体架构重构电源网络,大幅减少线路间电磁干扰,优化了功耗与性能的平衡。IMEC预测,背面供电技术将在A14至A10等更先进节点中持续深化,成为突破性能瓶颈的核心方案。

此外,IMEC还预测了2DFET(二维场效应晶体管)的未来发展。随着工艺节点向A2(0.2纳米)演进,基于单原子层2D材料的2DFET将取代CFET架构,推动芯片密度与性能实现指数级跃升。2D材料以其原子级厚度展现出独特优势,能够有效抑制短沟道效应,但同时也面临材料沉积、栅极叠层与介电沉积、低电阻源/漏接触等多方面的挑战。IMEC预计,到2039年,基于二维材料的第二代2DFET将成为主流,但实现这一目标仍需克服诸多技术难题。

总体而言,IMEC的半导体工艺路线图不仅展示了未来技术的发展方向,也揭示了半导体行业在设备、材料与工艺上面临的挑战。从FinFET到NanoSheet,从CFET到2DFET,每一次晶体管架构的革新都伴随着光刻技术、背面供电技术等领域的突破,推动芯片密度与性能不断跃升。然而,量子隧穿效应、2D材料制备难题、超精密光刻挑战等依然考验着行业的智慧,需要全行业在产学研协同创新的驱动下持续突破。

原文和模型

【原文链接】 阅读原文 [ 7045字 | 29分钟 ]

【原文作者】 半导体行业观察

【摘要模型】 deepseek-v3

【摘要评分】 ★★★★★